# FLEXデバイスを DSPコプロセッサとして使用する方法

テクニカル・ブリーフ-4

1996年2月

高性能のDSP(ディジタル信号処理)アプリケーションにプログラマブルなDSPプロセッサが使用された場合、DSPプロセッサのマルチプライヤ(乗算器)、アキュムレータまたはアダーハの各ファンクションが性能のボトルネックになることがあります。アルテラのFLEXデバイスをDSPコプロセッサとして使用することによって、ビデオ・コンボリュージョン、ケーブル・ネットワーク用の高周波通信システム、ダイレクト・シーケンス(DS)方式のスペクトラム拡散モデルなどのアプリケーションにおけるシステム性能を大幅に向かせることができます。FLEXデバイスによるDSPコプロセッサは高速で多数の演算を必要とするファンクションの動作を実行するため、DSPプロセッサを他のファンクションの動作に自由に使用できるようになります。

例: ダイレクト・シーケンス方式のスペクトラム拡散データ通信に使用したFLEX DSP

ダイレクト・シーケンス方式のスペクトラム拡散モデルは携帯電話やコードレス電話、またワイヤレスLANなどに使用されています。スペクトラム拡散のアプリケーションにおいては、送信機側でオリジナル信号に疑似ランダムのPNコードが乗算され、受信側のフィルタが同じPNコードを使って信号の相関をとります。

ワイヤレスLANのあるメーカーは16ビット40MHzのプログラマブルDSPプロセッサを使用して、これらの相関とQAM信号の復調機能を実現しました。この応用例では、相関動作のためにシステムが長い時間を必要としたため、全体のシステム性能が10MHzにとどまりました。このシステムが15ビットのPNコードのシーケンスに対して10MHzのシステム・スピードで動作するということは、このときのデータ・レートは1Mビット/秒(Mbps)以下に相当することになります。

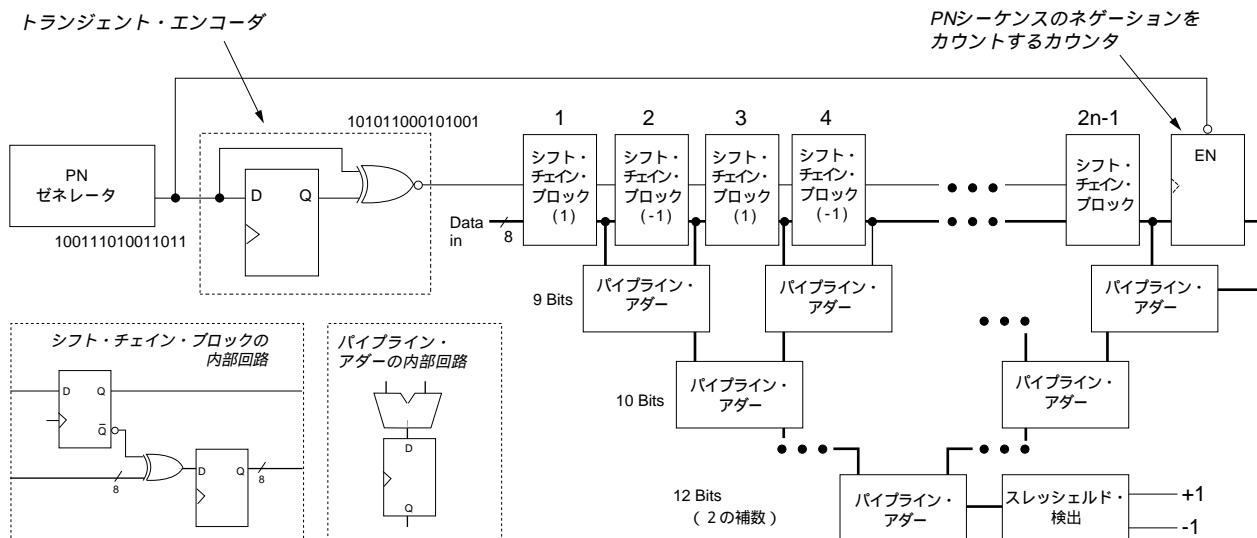

このシステムで、相関の動作を行わせるためにFLEXデバイスを追加し、プログラマブルDSPプロセッサにはデータ復調だけの動作を行わせることで、そのシステム性能が60MHzまで改善されました。FLEXデバイスを使用してパイプライン化されたアダーハサブトラクタを内蔵したFIRフィルタを構成し、相関の回路機能を実現した例を下図に示します。

FLEXデバイスで実現したスペクトラム拡散の受信適合フィルタ

Note: ネゲーションはシフト・チェイン内の単純なインバータによって処理される。次の式にしたがって、各ネゲーションに対するアダーハツリーに1を加えることによって、2の補数による表現が維持される:  $a+b-c-d=a+b+(!c+1)+(!d+1)=a+b+!c+!d+2$

プログラマブルDSPプロセッサで相関と復調の双方の機能を実現している場合、PNシーケンスの帯域が増大すると、このDSPプロセッサにはさらに高い性能が要求されます。これに対して、同じ機能をDSPプロセッサとFLEXデバイスで実現した場合は、FLEXデバイスのリソースをパラレルに加えていくことによって、PNコードの帯域を増大させることができました。このファンクションを31ビットのPNシーケンスに拡大した場合には、EPF8452AをEPF8636Aに変更する必要になりましたが、このシステムはプログラマブルDSPプロセッサ側のデザインを変更することなく、60MHzの動作速度を維持することができました。以上のように、FLEXデバイスを使用することによって、システムの性能を大幅に向上させることができました。

### ダイレクト・シーケンス方式のスペクトラム拡散通信システムの性能比較

| 使用デバイス                   | 実現した機能              | フィルタ・サイズ      | 性能    | 使用ロジック・サイズ   |

|--------------------------|---------------------|---------------|-------|--------------|

| 固定小数点のプログラマブルDSPプロセッサ    | 相関とデータ復調            | 15ビットのPNシーケンス | 10MHz | -            |

| アルテラのEPF8452A            | 相関<br>(15ビット・シーケンス) | 15ビットのPNシーケンス | 66MHz | 266個のロジック・セル |

| および固定小数点のプログラマブルDSPプロセッサ | データ復調               |               |       |              |

| アルテラのEPF8636A            | 相関<br>(31ビット・シーケンス) | 31ビットのPNシーケンス | 66MHz | 553個のロジック・セル |

| および固定小数点のプログラマブルDSPプロセッサ | データ復調               |               |       |              |

### DSPデザイン・キット

FLEXデバイスは柔軟性を犠牲にすることなく、高性能なプログラマブルDSPソリューションを提供します。アルテラは「DSPデザイン・キット」を提供しています。この「DSPデザイン・キット」には、各種のDSPファンクションを実現するときに使用できる、カスタマイズ可能なビルディング・ブロックが含まれています。提供されるビルディング・ブロックには、全並列型でデータと係数の幅を指定できるようになっている8、16、24、32および64タップのFIRフィルタ、さらに大きなタップ数を実現できる全直列型のフィルタ、浮動小数点演算ファンクションなどが含まれています。「DSPデザイン・キット」で提供されているこれらのファンクションはアルテラのFLEXアーキテクチャに最適化されており、各デザインで要求されるパラメータに応じてこれらのファンクションをカスタマイズすることができます。

---

さらに詳しい情報が下記の資料で提供されています。最後に表示されている記号は、各資料のドキュメント番号です。

#### プロダクト・インフォメーション・ブリティン

PIB 23 *Digital Signal Processing in FLEX Devices* (日本語版: FLEXデバイスによるデジタル信号処理) A-PIB-023-01

#### アプリケーション・ノート

AN 73 *Implementing FIR Filters in FLEX Devices* (日本語版: FLEXデバイスによるFIRフィルタの実現) A-AN-073-01

これらの資料は、日本アルテラおよび各販売代理店にご請求下さい。また、英文の資料については、アルテラのWWWサイト、<http://www.altera.com>からダウンロードすることができます。